Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

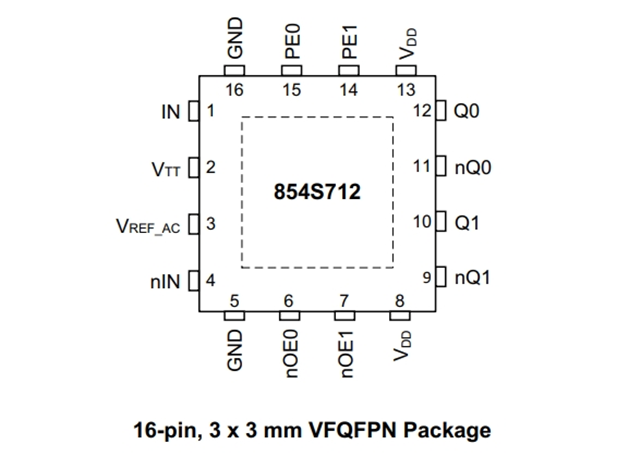

Clock Buffer 854S712AKILF Introduction: A 1:2 fan-out buffer with pre-weighting function

The 854S712AKILF is a clock buffer launched by Renesas, mainly used in scenarios where clock signal distribution or buffering is required. The following are its core parameters:Type: Fan-out buffer (allocated)Number of circuits: 1Ratio - Input: Output…

The 854S712AKILF is a clock buffer launched by Renesas, mainly used in scenarios where clock signal distribution or buffering is required. The following are its core parameters:

Type: Fan-out buffer (allocated)

Number of circuits: 1

Ratio - Input: Output: 1:2

Differential - Input: Output: Yes/Yes

Input: CML, LVDS, LVPECL

Output: LVDS

Frequency - Maximum: 3 GHz

Voltage - Power supply: 3.135V to 3.465V

Operating temperature: -40°C to 85°C

Installation type: Surface mount type

Package/Housing: 16-VFQFN

Introduction

The 854S712AKILF is a differential, high-speed 1:2 data/clock fan-out buffer and line driver. The output supports pre-emphasis to drive the backplane and long transmission lines, while reducing the interference effect between symbols. The pre-weighting level can be configured to optimize for low bit error rate or low power consumption. Pre-weighting uses an increased output voltage swing for the commutation position.

The 854S712AKILF is optimized for data rates up to 4.5Gbps (NRZ), deterministic jitter in data applications, and low additional jitter in clock applications. The output of the 854S712AKILF complies with the LVDS standard, while the differential input is compatible with various signal levels, such as LVDS, LVPECL and CML. Internal input termination, bias voltage output for AC coupling and small package (VFQFN) support space-saving circuit board design. The 854S712AKILF is powered by a 3.3V supply and supports an industrial temperature range of -40°C to 85°C.

Product features of 854S712AKILF

1:2 differential data/clock fan-out buffer and line driver

4.5 Gbps data rate (NRZ) (maximum value)

Differential LVDS output

Supports differential input for LVDS, LVPECL and CML levels

Configurable output pre-emphasis

Low skew output: 10ps (maximum)

Low data deterministic jitter: 4ps (maximum)

Control the level of the LVCMOS interface input

The asynchronous output is disabled and enters a high-impedance state

Internal input termination: 100? (Difference

Additional phase jitter, RMS: 0.08ps (typical value)

The full power supply voltage is 3.3V

Ambient operating temperature: -40°C to 85°C

Lead-free (RoHS 6) packaging is adopted

Application scenarios

The 854S712AKILF is suitable for scenarios that require clock signal distribution or buffering, such as:

High-speed digital circuit design

Clock management of communication equipment

Clock synchronization of industrial control systems

This device has been certified by the JESD-30 and JESD-609 standards, meeting the requirements of the electronics industry for the integrity of clock signals.

Supply information

For the purchase of 854S712AKILF clock buffers, please contact Mingjiada electronics (www.hkmjd.com).

Time:2025-08-28

Time:2025-08-28

![[STBR3012L2Y] Automotive High Voltage Rectifier for Bridge Applications, Diode 1200 V 30A](/upload/202508/28/202508281413132053.png)

Time:2025-08-28

Time:2025-08-28

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: