Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

HMC7044LP10BETR High Performance, 3.2 GHz, 14-Output Jitter Attenuator with JESD204B Interface

HMC7044LP10BETR: High-performance, 3.2GHz, 14-output jitter attenuator with JESD204B interfaceOverviewThe HMC7044 is a high-performance two-loop integer n-division jitter attenuator that selects frequencies to reference and generate ultra-low phase no…

HMC7044LP10BETR: High-performance, 3.2GHz, 14-output jitter attenuator with JESD204B interface

Overview

The HMC7044 is a high-performance two-loop integer n-division jitter attenuator that selects frequencies to reference and generate ultra-low phase noise, and supports high-speed data converters with parallel or serial (JESD204B type) interfaces.

The HMC7044 has two SPI selectable integer mode PLLS and overlapping on-chip VCO tuning ranges up to 2.5 GHz and 3 GHz, respectively. The device is designed to meet the requirements of GSM and LTE base station design and simplify the design of baseband and radio card clock trees with multiple clock management and allocation features. The HMC7044 provides 14 low-noise, configurable outputs that allow for flexible interface with many different devices, including data converters, field programmable gate arrays (FPgas), and mixer local oscillator (LO).

Applications

• The JESD204B clock is generated

Cellular infrastructure (multi-carrier GSM, LTE, W-CDMA)

• Data converter clock

• Microwave baseband card

• Phased array reference assignment

Features

Ultra-low rms jitter: Typical value: 44 fs (12 kHz to 20 MHz, 2457.6MHz)

Noise base: −156 dBc/Hz (2457.6MHz)

Low phase noise: −141.7 dBc/Hz (983.04 MHz output at 800 kHz)

PLL2 provides up to 14 LVDS, LVPECL or CML Device clocks (DCLK)

CLKOUTx/CLKOUTx and SCLKOUTx/SCLKOUTx have a maximum frequency of 3200 MHz

JESD204B is compatible with System Reference (SYSREF) pulses

25 ps analog delay and ½ VCO cycle digital delay, each of the 14 clock output channels can be programmed for delay

The relationship between phase noise and power consumption can be programmed by SPI

SYSREF valid interrupts simplify JESD204B synchronization

Narrow band, dual-core VCO

Up to 2 buffered voltage controlled oscillator (VCXO) outputs

Up to 4 input clocks in LVDS, LVPECL, CMOS, and CML modes

Frequency hold mode maintains the output frequency

Signal loss (LOS) detection and uninterrupted reference switching

4 GPIO alarm/status indicators to determine system health

Supports external VCO inputs up to 6000 MHz

On-chip regulators provide excellent PSRR

68 pin, 10 mm x 10 mm LFCSP package

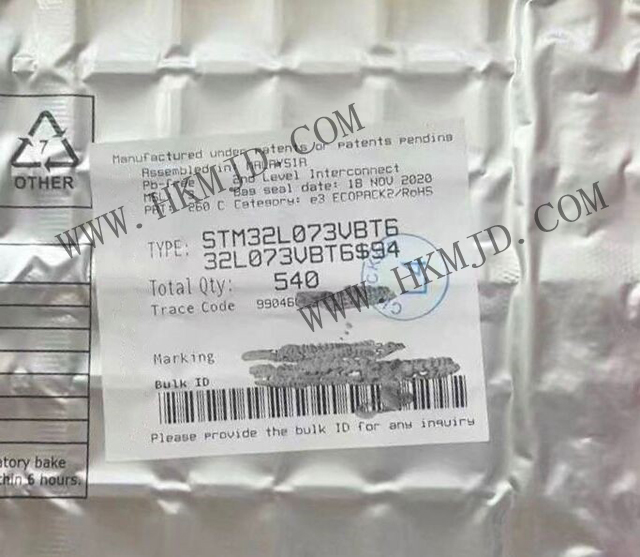

Shenzhen Mingjiada Electronics Co., Ltd. supply and demand HMC7044LP10BETR high-performance, 3.2GHz, 14-channel output jitter attenuator with JESD204B interface.

Please contact us if you need:

Contact: Mr. Chen

Tel: +8613410018555

Email: sales@hkmjd.com

![Supply Original [Renesas] R7F701412EABG RH850/D1M High-End Automotive Microcontrollers](/upload/202508/05/202508051606383139.jpg)

Time:2025-08-05

Time:2025-08-05

Time:2025-08-05

Time:2025-08-05

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: