Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest InformationChip introduction:The LTC2140CUP-14 is A two-channel simultaneous sampling 14-bit A/D converter designed for digital processing of high frequency, wide dynamic range signals. These devices are ideal for demanding communications applications with AC pe…

Chip introduction:

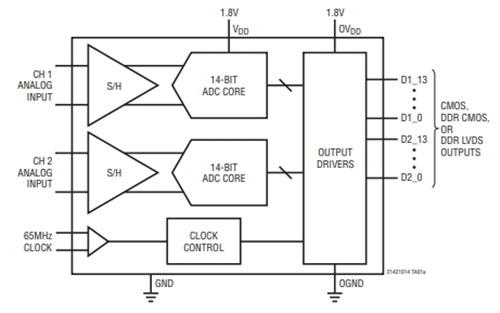

The LTC2140CUP-14 is A two-channel simultaneous sampling 14-bit A/D converter designed for digital processing of high frequency, wide dynamic range signals. These devices are ideal for demanding communications applications with AC performance including 73.2dB SNR and 90dB spurious free Dynamic range (SFDR). The ultra-low jitter of 0.08psRMS enables undersampling of the IF frequency and superior noise performance.

The DC specification includes ±1LSB INL (typical value), ±0.3LSB DNL (typical value), and no loss codes over the entire temperature range. The conversion noise is 1.2LSBRMS.

The digital output can be full rate CMOS, double data rate CMOS or double data rate LVDS. A separate output power supply provides CMOS output swing from 1.2V to 1.8V.

The ENC+ and ENC - inputs can be differentially or single-ended driven with a sine wave, PECL, LVDS, TTL, or CMOS input. An optional clock duty cycle stabilizer delivers high performance at full speed and multiple clock duty cycles.

Target application:

communication

Cell base station

Software-defined radio

Portable medical imaging

Multi-channel data acquisition

Nondestructive testing

Features:

Two-channel simultaneous sampling ADC

73.2dB SNR

90dB SFDR

Low power: 95mW / 67mW / 50mW (total value)

48mW / 34mW / 25mW (per channel)

Single 1.8V power supply

CMOS, DDR CMOS, or DDR LVDS output

Optional input range: 1VP-P to 2VP-P

750MHz Full Power bandwidth sampling and holding (S/H)

Optional data output random function generator

Optional clock duty cycle stabilizer

Downtime and nap mode

Serial SPI port for configuration

64 pin (9mm x 9mm) QFN package

Time:2025-07-08

Time:2025-07-08

![[Supply] IR2304STRPBF (Infineon) Half-Bridge Gate Driver IC With Shoot Through Protection](/upload/202507/08/202507081317524666.jpg)

Time:2025-07-08

Time:2025-07-08

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: