Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

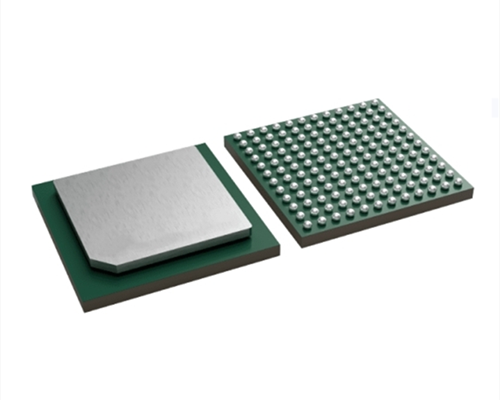

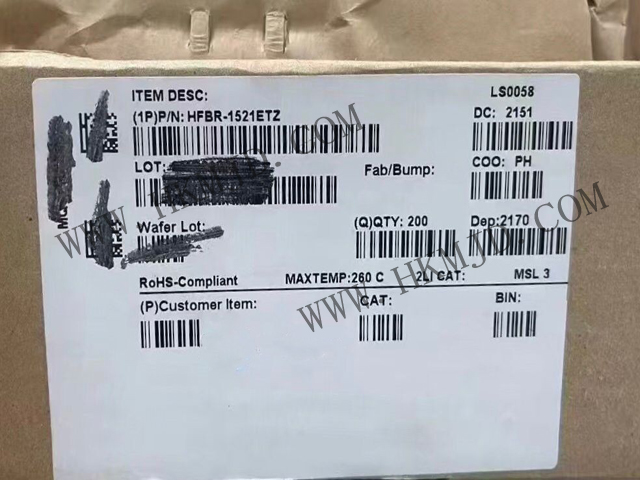

Sell ADC12QJ1600ALREP (TI) Quad 1.6G SPS 12-Bit Analog-to-Digital Converter (ADC)

The ADC12QJ1600ALREP is a quad, 12-bit, 1.6G SPS ADC.The low power consumption, high sample rate, and 12-bit resolution make it suitable for use in a variety of multichannel communication systems.

The ADC12QJ1600ALREP is a four-channel 1.6GSPS 12-bit analog-to-digital converter (ADC) with JESD204C interface.

Applications:

• Electronic warfare (signals intelligence, electronic intelligence)

• Satellite Communications (SATCOM)

• GPS/GNSS receiver

• Radar

Product Description:

The ADC12QJ1600ALREP is a four-channel, 12-bit, 1.6GSPS analog-to-digital converter (ADC). With low power consumption, high sampling rate and 12-bit resolution, the device is suitable for use in various multi-channel communication systems.

The 6GHz full power input bandwidth (-3dB) also supports direct RF sampling in the L and S bands.

The JESD204C serial interface reduces system size by reducing the amount of printed circuit board (PCB) wiring. The interface mode supports 2 to 8 channels (dual-channel and quad-channel devices) or 1 to 4 channels (single-channel devices) and serializer/deserializer baud rates up to 17.16Gbps, enabling optimal configuration for each application.

Features:

• High reliability enhanced products:

- Controlled baseline

- Same assembly and test site

- Same manufacturing site

- Temperature range from -55°C to 125°C

- Extended product life cycle

- Extended product change notice

- Product traceability

• ADC core:

- Resolution: 12 bits

- Maximum sampling rate: 1.6GSPS

- Non-interleaving architecture

- Internal jitter reduces high harmonics

• Performance specifications (-1DBFS) :

- SNR (100MHz) : 57.4dBFS

- ENOB (100MHz) : specifies 9.1 bits

- SFDR (100MHz) : 64dBc

- Background noise (-20dbfs) : -147dbfs

• Full scale input voltage: 800mVP-DIFF

• Full power input bandwidth: 6GHz

• JESD204C Serial data interface:

- Support a total of 2 to 8 serializer/deserializer channels

- Max baud rate: 17.16Gbps

- 64B/66B and 8B/10B encoding modes

- Subclass 1 supports deterministic delay

- Compatible with JESD204B receiver

• Optional internal sampling clock generation

- Internal PLL and VCO (7.2-8.2GHz)

• The SYSREF window simplifies synchronization

• Four clock outputs simplify the system clock

- Reference clock of the FPGA or adjacent ADC

- Reference clock of the serializer/deserializer transceiver

• Timestamp input and output of the pulse system

• Power consumption (1GSPS) : 1.9W

• Power supply: 1.1V/1.9V

Time:2025-07-10

Time:2025-07-10

Time:2025-07-10

Time:2025-07-10

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: