Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

The ADRF6821ACPZ from Analog Devices is a DPD RFIC with an integrated fractional-N PLL and VCO

Overview:The ADRF6821ACPZ from ADI is a highly integrated dual radio frequency (RF) input, zero intermediate frequency (IF)/ low IF RFIC receiver. It has an quadrature demodulator, a digital step attenuator (DSA), an IF linear amplifier, an integrated…

Overview:

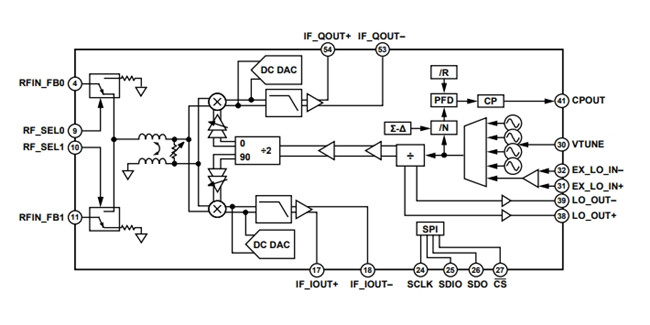

The ADRF6821ACPZ from ADI is a highly integrated dual radio frequency (RF) input, zero intermediate frequency (IF)/ low IF RFIC receiver. It has an quadrature demodulator, a digital step attenuator (DSA), an IF linear amplifier, an integrated fractional frequency PLL (PLL) and a low-phase noise multi-core voltage-controlled oscillator (VCO). RFIC is ideal for digital predistortion (DPD) system communication.

The device features a highly isolated 2:1 RF switch and on-chip wideband RF balun that supports two single-ended 50 Ω terminated RF inputs. The programmable attenuator ensures that the high linearity demodulator core has a premium differential RF input level. The integrated attenuator provides a attenuation range of 15 dB with a step size of 1 dB. The high linearity IF amplifier follows the demodulator and provides an interface to the next component in the chain, usually the analog-to-digital converter (ADC).

The ADRF6821 provides two ways to generate a differential local oscillator (LO) input signal: internally via an on-chip fractional frequency synthesizer with a low-phase-noise VCO, or externally via a phase-noise LO signal. The integrated synthesizer has a continuous LO coverage range of 450 MHz to 2800 MHz. The PLL reference input supports a wide frequency range and has an integrated reference divider before the phase frequency detector (PFD).

Block diagram of ADRF6821ACPZ:

Features:

DPD receiver with integrated fractional PLL

RF input frequency range: 450 MHz to 2800 MHz

Internal LO input frequency range: 450 MHz to 2800 MHz

Dual RF input with SPDT absorption RF switch

The integrated RF balun is suitable for single-ended 50Ω inputs

The integrated VCO covers the entire RF input range

Digitally programmable LO phase offset and dc zeroing

Programmable via 4-wire SPI

56 Pin 8 mm x 8 mm LFCSP

Applications:

Cellular W-CDMA/GSM/LTE

DPD receiver

Microwave point-to-point radio

Time:2025-07-03

Time:2025-07-03

Time:2025-07-03

Time:2025-07-03

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: