Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest InformationTo date, the technical development of Rambus DDR5 has focused on high-capacity server memory modules (RDIMMs), including a register clock driver (RCD), a power management chip (PMIC), a serial detection Hub (SPD Hub), and two independent temperature s…

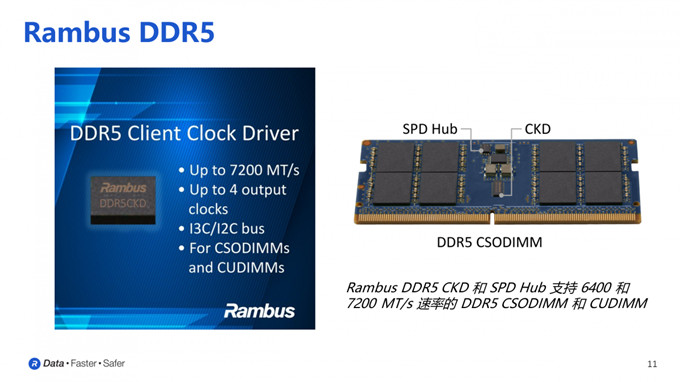

To date, the technical development of Rambus DDR5 has focused on high-capacity server memory modules (RDIMMs), including a register clock driver (RCD), a power management chip (PMIC), a serial detection Hub (SPD Hub), and two independent temperature sensors at both ends of the DIMM. Rambus is bringing its advances in server technology to the client market with the announcement of DDR5 Client Clock drivers (CKD) for the next generation of high-performance desktop and notebook computers.

CKD value

John Eble, vice president of product marketing for Rambus's Memory Interconnect chip business unit, said that as speeds get higher, the amount of jitter introduced per unit bit time increases due to factors such as power supply, induced jitter crosser, and jitter amplification through attenuation, making it a real challenge to converge the timing budget for a synchronized memory interface.

As shown on the left side of the figure below, neither the unbuffered DIMMs for desktops and workstations nor the SO-DIMMs for laptops have the logic circuit to enhance signal integrity, and the CPU drives up to four differential clocks directly to the DIMM and the DRAM collection on that module. However, the clock originates from a very power consuming SoC with a lot of power noise, and the clock signal needs to escape the dense CPU pin area, travel through the motherboard, and up to the DIMM slot to the target DRAM.

The DDR5 client clock driver highlighted in blue on the right is a signal integrity timing enhancement chip. It can restore the clock amplitude and timing fidelity of the individual DRAM on the DIMM. In single-phase lock-loop mode, the CKD receives a single clock from the CPU, recovers the clock amplitude, reduces jitter via a phase-locked loop (PLL), and then outputs four clean copies. In addition, CKD replaces the need for up to 4 connections from the CPU to the module, thereby reducing CPU pins and power consumption and simplifying motherboard wiring.

Since the DDR5 module is dual-channel, there is also a dual PLL mode (where the two halves of the DIMM can operate independently of each other) and a clock PLL bypass mode for backward compatibility. The Rambus DDR5 CKD and SPD Hub are part of the new client memory interface chip offerings and a key differentiator for client DIMMs.

The industry generally uses 6400MT/s as the dividing line, and DIMMs higher than this rate are called CUDIMMs and CSODIMMs. The CUDIMM concept is largely a scaled-down version of RDIMMs, which have been used in servers for many years, with the difference that RDIMMs buffer clock signals, command, and address bus signals, while CKD in CUDIMMs only buffers clock signals. But the advent of CuDIMMs will help install more powerful DDR5 memory on PCS, allowing modern AI applications to run with sufficient bandwidth and performance.

Supports DDR5 DIMMs with data rates up to 7200MT/s

Although CKD chips are not required in DDR5 client memory modules with data rates of 4800 and 5600MT/s, all client modules with rates higher than 6400MT/s require CKD for buffering and retiming the clock. Therefore, the new DDR5 client clock driver products support CUDIMMs and CSODIMMs at speeds up to 7200MT/s for future generations of client devices.

John Eble believes that one of the main advantages of the Rambus DDR5 CKD is the ultra-low jitter clock. It is the low random jitter and low deterministic jitter provided by this scheme for DRAM that increases the overall system timing path margin, which is important for achieving high rates.

Other advantages or values brought by the device include a higher amplitude clock, resulting in a greater voltage margin on DRAM. CKD can potentially reduce system power consumption and ease board wiring challenges by eliminating the extra clock in the CPU. In addition, CKD includes a low-power standby mode and dual-channel PLL mode to optimize system performance and efficiency, which is critical for laptop systems.

These high-bandwidth DIMMs will be introduced to desktops and laptops first, as they require the highest levels of performance to support AI, gaming, and content creation. At the same time, Rambus also offers a chipset solution for client-side DIMMs, which integrates CKD devices and SPD hubs to meet the new memory requirements of future AIpcs.

In single PLL mode, CKD will receive a clock; Two clocks can be received in dual PLL mode and up to four high-precision output clocks can be driven depending on DRAM capacity and configuration. CKD can be configured and pulled through its I2C and I3C sideband interface, which is buffered by the SPD Hub. Currently, Rambus is actively supporting multiple generations of DDR5 RCDS, each associated with a specific DIMM speed.

"As with any new technology, we see that these new modules with CKD will first find application in systems that require high memory bandwidth." As AI-enabled applications become more prevalent and speeds of 6400MT/s or higher become mainstream, PC memory performance requirements continue to increase, and the number of systems using CKD will grow significantly over time. "John Eble said.

According to the plan, the DDR5 roadmap plans for data transfer rates of up to 8400MT/s for native DRAM devices. But we've seen an interesting breakthrough technology on the server side that uses multiplexing to extend the bandwidth cap and deliver higher bandwidth on each memory slot. JEDEC has announced the latest MRDIMM, which will use native DDR5 6400MT/s DRAM devices. With multiplexing, MRDIMM is able to extend bandwidth up to 12.8Gbps.

As DDR5 DRAM speeds expand beyond 6400 MT/s, the same multiplexing technology can be used to further increase the bandwidth of DIMM memory slots. But as data rates get higher and higher, the available timing budget for maintaining synchronous operations in memory systems gets smaller and smaller, so timing accuracy needs to continue to improve on an absolute scale.

Company homepage www.hkmjd.com

Time:2025-08-19

Time:2025-08-19

![Mingjiada Supply [ADI] LT3502AEDC 500mA, Step-Down DC/DC Regulators](/upload/202508/19/202508191511211474.jpg)

Time:2025-08-19

Time:2025-08-19

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: