Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

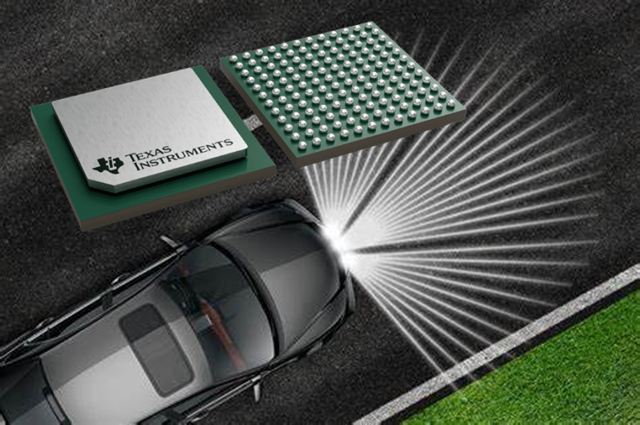

TI Analog-to-Digital Converter (ADC) ADC12DJ1600AAVQ1 Automotive 2-channel, 12-bit, 1.6GSPS ADC

ADC12DJ1600AAVQ1 - Automotive 2-channel, 12-bit, 1.6GSPS ADC with JESD204C interface and integrated sampling clock generatorOverviewThe ADC12XJ160-Q1 is a series of 12-bit, 1.6-Gsps four-channel/dual-channel/single-channel analog-to-digital converters…

ADC12DJ1600AAVQ1 - Automotive 2-channel, 12-bit, 1.6GSPS ADC with JESD204C interface and integrated sampling clock generator

Overview

The ADC12XJ160-Q1 is a series of 12-bit, 1.6-Gsps four-channel/dual-channel/single-channel analog-to-digital converters (ADCs) that are ideal for optical detection and ranging (LiDAR) systems due to their low power consumption, high sampling rate and 12-bit resolution. The ADC12xJ1600-Q1 meets the standards for automotive applications.

The JESD204C serial interface reduces system size by reducing the amount of printed circuit board (PCB) wiring. The interface mode supports 2 to 8 channels (dual-channel and quad-channel devices) or 1 to 4 channels (single-channel devices) and serializer/deserializer baud rates up to 17.16Gbps, enabling optimal configuration for each application.

Features

• Complies with AEC-Q100 standard for automotive applications:

- Temperature Class 1: -40 °C to +125°C, TA

• ADC core:

- Resolution: 12 bits

- Maximum sampling rate: 1.6GSPS

- Non-interleaving architecture

- Internal jitter reduces high harmonics

• Performance specifications (-1DBFS) :

- SNR (100MHz) : 57.4dBFS

- ENOB (100MHz) : specifies 9.1 bits

- SFDR (100MHz) : 64dBc

- Background noise (-20dbfs) : -147dbfs

• Full scale input voltage: 800mVP-DIFF

• Full power input bandwidth: 6GHz

• JESD204C Serial data interface:

- A total of 2 to 8 (four channel/two channel) or 1 to 4 (single channel) serializer/destringer channels are supported

- Max baud rate: 17.16Gbps

- 64B/66B and 8B/10B encoding modes

- Subclass 1 supports deterministic delay

- Compatible with JESD204B receiver

• Optional internal sampling clock generation

- Internal PLL and VCO (7.2-8.2GHz)

• The SYSREF window simplifies synchronization

• Four clock outputs simplify the system clock

- Reference clock of the FPGA or adjacent ADC

- Reference clock of the serializer/deserializer transceiver

• Timestamp input and output of the pulse system

• Power consumption (1GSPS) :

- Four channels: 477mW per channel

- Dual-channel: 700mW per channel

- Single channel: 1000mW

• Power supply: 1.1V/1.9V

Application

• Laser Radar (LiDAR)

Time:2024-11-19

Time:2024-11-19

![Supply [Infineon] Power MOSFET: Automotive MOSFET, N/P-Channel Power MOSFET, SiC CoolSiC™ MOSFET](/upload/202411/19/202411191525203061.jpg)

Time:2024-11-19

Time:2024-11-19

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: