Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

8A34043E-000NBG8 Universal Frequency Translator IC with Four Independent Timing Channels

Supply Renesas 8A34043E-000NBG8 Universal frequency Converter IC with four independent timing channels!Instructions:The Renesas/IDT 8A34043 four-channel universal frequency converter can generate synchronous or asynchronous clocks from its reference i…

Supply Renesas 8A34043E-000NBG8 Universal frequency Converter IC with four independent timing channels!

Instructions:

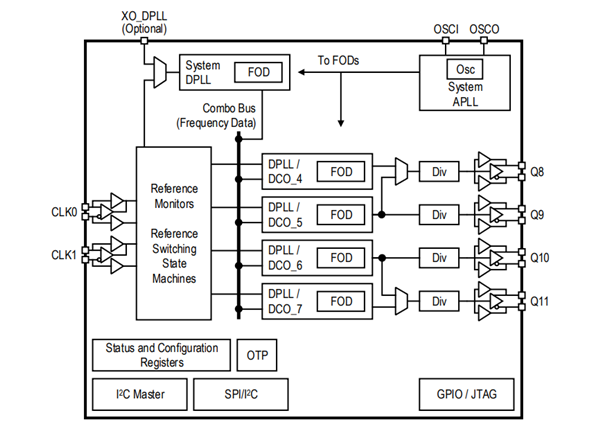

The Renesas/IDT 8A34043 four-channel universal frequency converter can generate synchronous or asynchronous clocks from its reference input. These converters have a variety of tools for managing timing references, clock transitions, and timing paths for common communication protocols. In addition, the device supports multiple independent timing channels for clock generation, jitter attenuation, and universal frequency conversion.

The 8A34043 can be used to synchronize communication ports, line cards, or subcards connected to the synchronization source through the backplane or other media. Input-to-input, input-to-output, and output-to-output phase offsets can be precisely managed. The device outputs an ultra-low jitter clock and can directly synchronize SERDES operating at speeds up to 28Gbps, including CPRI/OBSAI, SONET/SDH, and PDH interfaces. The 8A34043 converter is ideal for use in any synthesizer or jitter attenuator application, including Optical Transport Network (OTN) and Synchronous Ethernet (SyncE) systems.

Features:

Four separate timing channels

Jitter output below 150fs RMS (typical)

Digital PLL (DPLL) locks to any frequency between 1kHz and 1GHz

DPLL/ Numerical Control oscillator (DCO) produces any frequency between 0.5Hz and 1GHz

The DCO output can be phase-aligned and frequency-aligned with the output of any DPLL or DCO

Supports up to 8 differential or 16 single-ended reference clock inputs

The device requires either a crystal oscillator or a fundamental harmonic crystal: 25MHz to 54MHz

Supports up to 12 differential outputs or 24 LVCMOS outputs

The reference monitor qualifies/disqualifies references based on LOS, activity, frequency monitoring, and/or LOS input pins

The automatic reference selection state machine selects the active reference for each DPLL based on the reference monitor, priority table, reply/non-reply, and other programmable Settings

The optional XO_DPLL input supports a wider range of XO, TCXO or OCXO frequencies (1MHz to 150MHz) for applications that require a local oscillator with high stability

The serial processor port supports 1MHz I2C or 50MHz SPI

The device can be automatically configured after reset by:

Built-in customer programmable one-time programmable memory

Standard external I2C EPROM implemented via a separate I2C master port

Applications:

• Core and access IP switches/routers

• Synchronize Ethernet devices

• 10Gb, 40Gb, and 100Gb Ethernet ports

• Wireless infrastructure for 4.5G and 5G network devices

• OTN multiplex transponders and line cards

8A34043E-000NBG8 functional block diagram

Time:2025-07-08

Time:2025-07-08

Time:2025-07-08

![Supply [Infineon] AIROC™ Wi-Fi Connected MCU, AIROC™ Bluetooth LE, Wi-Fi 6 Combo](/upload/202507/08/202507081447596589.jpg)

Time:2025-07-08

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: