Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

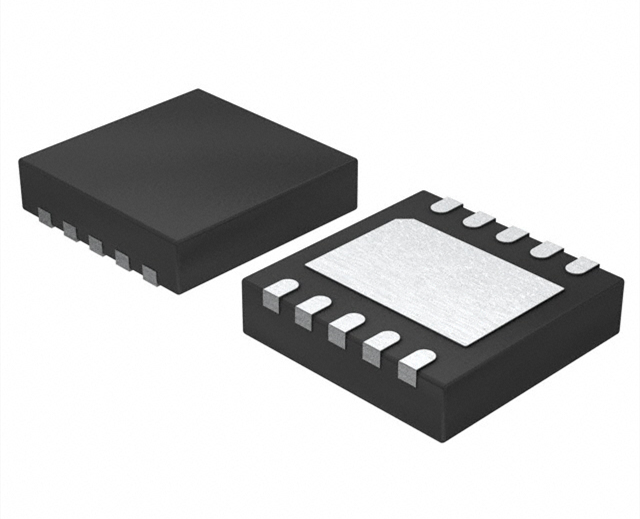

Broadcom Introduces Industry's First Dual 400G MACSec PHY [BCM81343A0IFSBG]

Broadcom Corporation introduces the industrys first dual 400G MACSec PHY for hyperscale data centers and cloud infrastructure. The BCM81343 chip is a dual 400G MACSec PHY with AES-256 designed to meet the security requirements of high-speed interconne…

Broadcom Corporation introduces the industry's first dual 400G MACSec PHY for hyperscale data centers and cloud infrastructure. The BCM81343 chip is a dual 400G MACSec PHY with AES-256 designed to meet the security requirements of high-speed interconnections in modern network infrastructures including hyperscale, cloud, service provider and enterprise networks. The BCM81343 expands on the previous generation's dual 100G MACSec PHY with a dual bandwidth 400G port that trips switching bandwidth capabilities and supports the IEEE 1588 Precise Time Protocol (PTP) to provide accurate clock timing for time-sensitive transactions and mission-critical tasks.

Broadcom BCM81343A0IFSBG is a 16nm low-power, high density PHY that integrates IEEE 802.1AE MACSec GCM-AES-256b encryption, IEEE 1588, retimer, reverse gear box, and equalizer capabilities. Supports 400 Gigabit Ethernet (400GbE), 200GbE, 100GbE, 50GbE, 40GbE, 25GbE, and 10GbE applications. The BCM81343 is designed for CDAUI8 and CDAUI4 electrical interfaces supporting QSFP-DD and OSFP optical modules.

Features:

Support the 25 g / 10 g / 40 g / 50 g / 100 g / 200 g / 400 g Ethernet applications

Supports 400GbE ports, with CDAUI8 to CDAUI8 interfaces, suitable for QSFP-DD, OSFP retiming /MACSec encryption applications

Supports 200GbE ports and CDAUI4 to CDAUI4 for QSFP56 retiming /MACSec encryption applications

MACSec is supported in reverse mode

2x50G PAM4 to 4x25G NRZ

Supports 100GbE, CAUI4 to CAUI4, for QSFP28 retiming /MACSec encryption applications

Support for IEEE 1588 enables Class C systems to meet stringent 5G timing requirements, as well as ITU-T Y.1731 Synchronous Ethernet (SyncE) recovery clock output

Supports FEC for all data rates up to 400G

16nm process node

Applications:

• Support for IEEE 802.1AE(Data Plane) and IEEE 802.1AEbw, including GCS-AES-256

• High-speed 10G/25G/40G/50G/100G/200G/400G MACSec encryption on the front panel line card

More products are available on the company's official website, welcome to visit: www.hkmjd.com

Time:2025-07-04

Time:2025-07-04

Time:2025-07-04

Time:2025-07-04

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: