Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

[Available] AD9528BCPZ-JESD204B/JESD204C Clock Generator with 14 LVDS/HSTL Output

The AD9528BCPZ is a JESD204B/JESD204C clock generator launched by (ADI), featuring an LFCSP-72 package and supporting multi-device synchronization. The following are its core features:14-channel output, configurable as HSTL or LVDSMaximum output frequ…

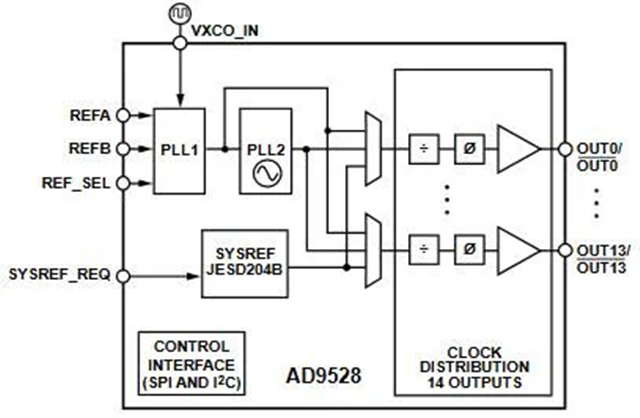

The AD9528BCPZ is a JESD204B/JESD204C clock generator launched by (ADI), featuring an LFCSP-72 package and supporting multi-device synchronization. The following are its core features:

14-channel output, configurable as HSTL or LVDS

Maximum output frequency

6 output channels up to 1.25GHz

8-channel output up to 1 GHz

It depends on the frequency accuracy of the voltage-controlled crystal oscillator (VCXO) (starting frequency accuracy: <±100 ppm)

Each output channel is equipped with a dedicated 8-bit divider

Coarse adjustment delay: 63 steps, each half the output frequency of the RF VCO divider, are not affected by jitter

Fine-tuning delay: 15 steps, resolution 31 ps

Typical output skew: 20 ps

Provide duty cycle correction for odd-numbered divider Settings

Output 12 and Output 13, VCXO output when powered on

Absolute output jitter: <160 fS (at 122.88 MHz)

Integration range from 12 kHz to 20 MHz

Digital frequency locking detection

SPI and I2C compatible serial control ports

Dual PLL architecture

PLL1

The reference input clock is reset to zero using an external VCXO

Phase detector rate: up to 110 MHz

Redundant reference input

Automatic and manual reference switching modes

Switching between recovery and non-recovery modes

The hold mode supports reference loss detection

The low-noise LVDS/HSTL output provided by VCXO can be used in RF/ intermediate frequency (RF/IF) frequency synthesizers

PLL2

Phase detector rate: up to 275 MHz

Integrated low-noise VCO

For details

The AD9528BCPZ is a two-stage PLL with an integrated JESD204B/JESD204C SYSREF generator, which can be used for multi-device synchronization. The first-stage phase-locked loop (PLL) (PLL1) achieves input reference voltage conditioning by reducing the jitter of the system clock. The second-level PLL (PLL2) provides a high-frequency clock, enabling lower integration jitter and lower wideband noise from the clock output driver. The external VCXO provides the low-noise reference voltage required by PLL2 to meet the demanding phase noise and jitter requirements and achieve acceptable performance. The tuning frequency range of the on-chip VCO is from 3.450 GHz to 4.025 GHz. The integrated SYSREF generator outputs single, N or continuous signals and synchronizes them with the PLL1 and PLL2 outputs to align The Times of multiple devices.

The AD9528BCPZ generates six outputs with a maximum frequency of 1.25 GHz (Output 0 to Output 3, Output 12 and Output 13), as well as eight outputs with a maximum frequency of up to 1 GHz. Each output can be configured to directly output from the PLL1, PLL2 or the internal SYSREF generator. Each of the 14 output channels contains a crossover with digital phase coarse adjustment function and an analog fine-tuning phase delay module, allowing all 14 output channels to have a high degree of flexibility in timing alignment. The AD9528BCPZ can also be used as a flexible dual-channel input buffer to enable the distribution of 14 device clock and/or SYSREF signals. At startup, the AD9528BCPZ directly sends VCXO signals to output 12 and Output 13, which are used as the startup ready clock.

Typical applications

High-performance wireless transceiver

LTE and multi-carrier GSM base stations

Wireless and broadband infrastructure

Medical instruments

Provide clocks for high-speed ADC, DAC, DDS, DDC, DUC and MxFE; Supports JESD204B/JESD204C

Low-jitter and low-phase noise clock distribution

Automatic test equipment (ATE) and high-performance instruments and meters

Basic parameters

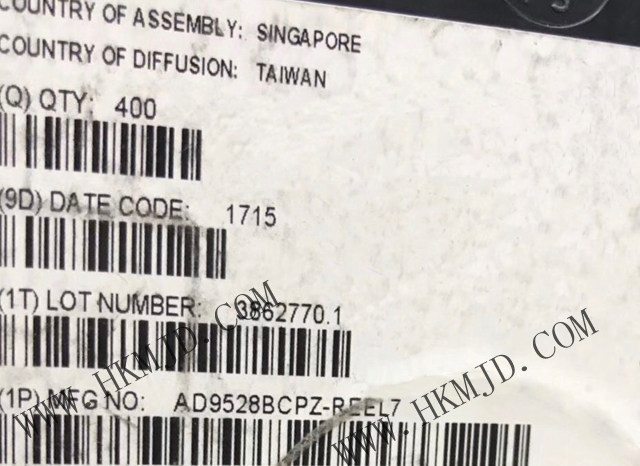

Product: AD9528BCPZ

PLL: With bypass

Input: CMOS, HSTL, LVDS

Output: HSTL, LVDS

Number of circuits: 1

Ratio - Input: Output: 2:14

Differential - Input: Output: Yes/Yes

Frequency - Maximum: 1.25GHz

Frequency divider/frequency doubler: Yes/No

Voltage - Power supply: 3.135V to 3.465V

Operating temperature: -40°C to 85°C

Installation type: Surface mount type

Device packaging: 72-LFCSP-VQ (10x10)

Act now and visit the official website of mingjiada electronics (www.hkmjd.com) to check the inventory and purchase quotations of AD9528BCPZ.

Time:2025-09-06

Time:2025-09-06

Time:2025-09-06

Time:2025-09-06

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: