Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

Microchip introduces PCI11101-I/MXX PCIe switches with USB3.2 host controllers

The PCI11101-I/MXX is a PCIe switch with integrated USB 3.2 Generation 2 host controller and programmable I/O.Description:The Microchip PCI11101 PCIe switch (with USB 3.2 host controller) combines a USB 3.2 Gen 2 host controller with programmable I/O.…

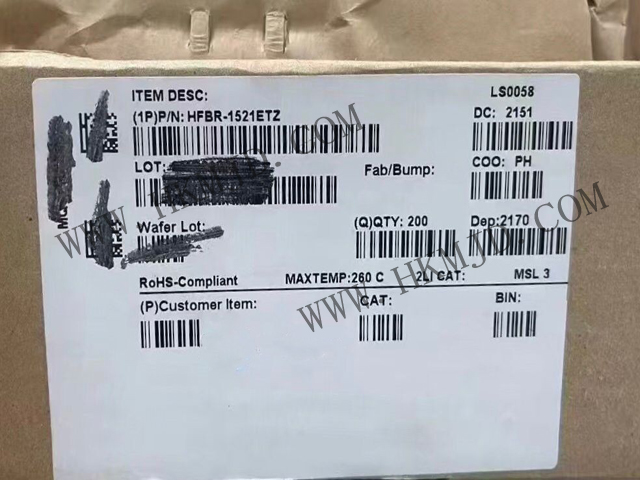

The PCI11101-I/MXX is a PCIe switch with integrated USB 3.2 Generation 2 host controller and programmable I/O.

Description:

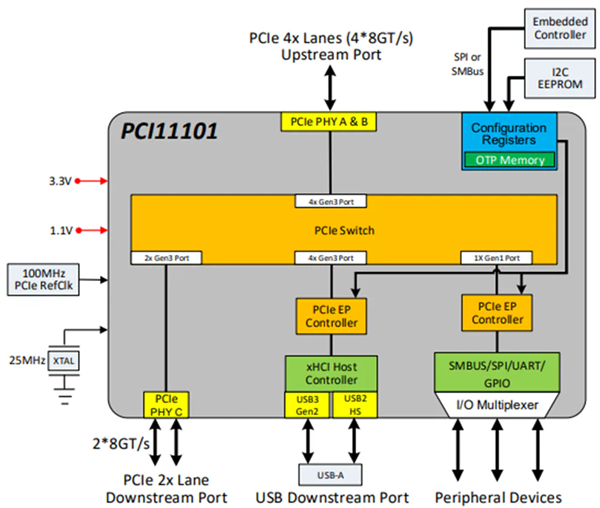

The Microchip PCI11101 PCIe switch (with USB 3.2 host controller) combines a USB 3.2 Gen 2 host controller with programmable I/O. The device has a 4-channel (4x8GT/s) uplink port and a 2-channel (2x8GT/s) downlink port to meet the needs of higher bandwidth PCIe subsystems for embedded applications. The device is certified for GEN4 compliance in the PCIe version 4.x specification and can use one or more channels for PCIe uplink, enabling a flexible system architecture. The PCI11101 ensures PCIe compliance from external interfaces to switching structures and endpoint controllers.

Features:

Integrated PCI switch architecture

Maximum payload: 512 bytes

Integrated PCIe physical interface

4 channel (4x8GT/s) uplink port

Supports single-channel, dual-channel, or four-channel links

2 channels (2x8GT/s) downstream port

Integrated USB 3.2 Gen 2 (10Gbps) physical interface

Integrated xHCI USB 3.2 Gen 2 (10Gbps) USB host controller

10Gbps Gen 2 PHY

USB HS/FS/LS PHY

Two external power supplies: +3.3V, +1.1V

Comprehensive power management capabilities

PCIe 3.1 Low Power Mouse Status (LPSS) L2 (with AUX Power)

Power and I/O

Integrated power-on reset circuit with configurable undervoltage/overvoltage protection

The blocking performance exceeds 150mA and complies with EIA/JESD 78 Class II standards

JEDEC 3A ESD performance

UART

Product evaluation board for RS232/RS485

Automatic direction control

Supports standard and advanced speeds

Basic or full signal support

Other functions

Multifunctional GPIO

Programmable pin multiplexer

Ability to use low-cost 25MHz crystals or clocks to reduce BOM

SPI peripheral interface

SMBus Indicates the target interface

SMBus Interface of the controller

PVT sensor

JTAG TAP

encapsulation

Lead-free, RoHS compliant 132-pin DRQFN package

Environmental condition

Commercial and industrial grades are available

PCI11101-I/MXX block diagram:

Applications:

Mathematical unloading

Visual Intelligence/Camera/Machine vision

Server with NG BMC and no PCH

Time:2025-07-10

Time:2025-07-10

Time:2025-07-10

Time:2025-07-10

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: