Welcome Here Shenzhen Mingjiada Electronics Co., Ltd.

sales@hkmjd.com

sales@hkmjd.com

Service Telephone:86-755-83294757

Latest Information

Latest Information Home

/Company Dynamics

/

Home

/Company Dynamics

/

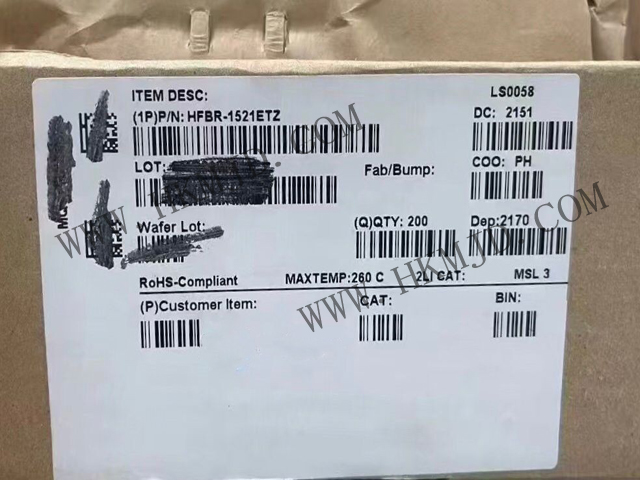

Designed to meet Ethernet-based network applications, TI LMK5B33414RGCR Network Synchronizer

The LMK5B33414RGCR device is a 14-way output, three DPLL and APLL network synchronizer with an integrated 2.5GHz bulk acoustic wave VCO with a timing accuracy of less than 5ns (Class D) designed to meet the stringent requirements of Ethernet-based net…

The LMK5B33414RGCR device is a 14-way output, three DPLL and APLL network synchronizer with an integrated 2.5GHz bulk acoustic wave VCO with a timing accuracy of less than 5ns (Class D) designed to meet the stringent requirements of Ethernet-based networking applications.

Instructions:

The LMK5B33414 Network synchronizer integrates three DPLLS to provide interruption-free switching and jitter attenuation over programmable loop bandwidth without the need for an external loop filter for greater flexibility and ease of use. Each DPLL phase locks the paired APLL to the reference input.

APLL3 features an ultra-high performance PLL using TI's proprietary bulk acoustic wave (BAW) technology to generate an output clock with 42fs (typical value) /60fs (maximum value) RMS jitter at 312.5MHz, independent of the frequency and jitter characteristics of the DPLL reference input. APLL2 and APLL1 provide options for the second or third frequency domain and/or synchronization domain.

The reference verification circuit monitors the DPLL reference clock and performs uninterrupted switching between clocks when a switching event is detected. Zero delay and phase elimination can be enabled to control the phase relationship from input to output.

The device can be fully programmed via an I2C or SPI interface. Onboard EEPROM can be used to customize the system startup clock. The device also has a factory default ROM configuration file as an alternate option.

Features of LMK5B33414RGCR:

• Ultra-low jitter Ethernet clock based on BAW VCO

- When the frequency is 312.5MHz, the typical value of RMS jitter is 42fs and the maximum value is 60fs

- When the frequency is 156.25MHz, the typical value of RMS jitter is 47fs and the maximum value is 65fs

Three high-performance digital phase-locked loops (DPLL) are paired with analog phase-locked loops (APLL)

- Programmable DPLL loop bandwidth ranges from 1mHz to 4kHz

- DCO frequency adjustment step < 1ppt

• 4 differential or single-ended DPLL inputs

- 1Hz (1PPS) to 800MHz input frequency

- Digital hold and uninterrupted switching

14 differential outputs in programmable HSDS/LVPECL, LVDS and HSCL output formats

- When configured with 6 LVCMOS frequency outputs and 12 differential outputs on OUT0_P/N, OUT1_P/N, GPIO1 and GPIO2, up to a total of 18 frequency outputs

- Supports programmable swing and common-mode output frequencies from 1Hz (1PPS) to 1250MHz

- Meets PCIe Generation 1 to 6 standards

• I2C or 3-wire / 4-wire SPI interface

Application of LMK5B33414RGCR:

• Wired network

- Data center interconnection or internal interconnection

- Timing card

- Line card

- Fixed card (Pizza box)

• SyncE (G.8262), SONET/SDH (Stratum 3/3E, G.813, GR-1244, GR-253), IEEE 1588 PTP auxiliary clock

• Jitter cancellation, drift attenuation and reference clock generation for 56G/112G PAM-4 serializer/deserializer

• 100G-800G data center switches, core routers, edge routers, WLAN

• Data center and enterprise computing

- Intelligent Network Interface Card (NIC)

• Optical Transmission Network (OTN G.709)

• Broadband fixed line access

• Industry

- Test and measure

- Medical Imaging

Time:2025-07-10

Time:2025-07-10

Time:2025-07-10

Time:2025-07-10

Contact Number:86-755-83294757

Enterprise QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

Business Hours:9:00-18:00

E-mail:sales@hkmjd.com

Company Address:Room1239, Guoli building, Zhenzhong Road, Futian District, Shenzhen, Guangdong

CopyRight ©2022 Copyright belongs to Mingjiada Yue ICP Bei No. 05062024-12

Official QR Code

Links: